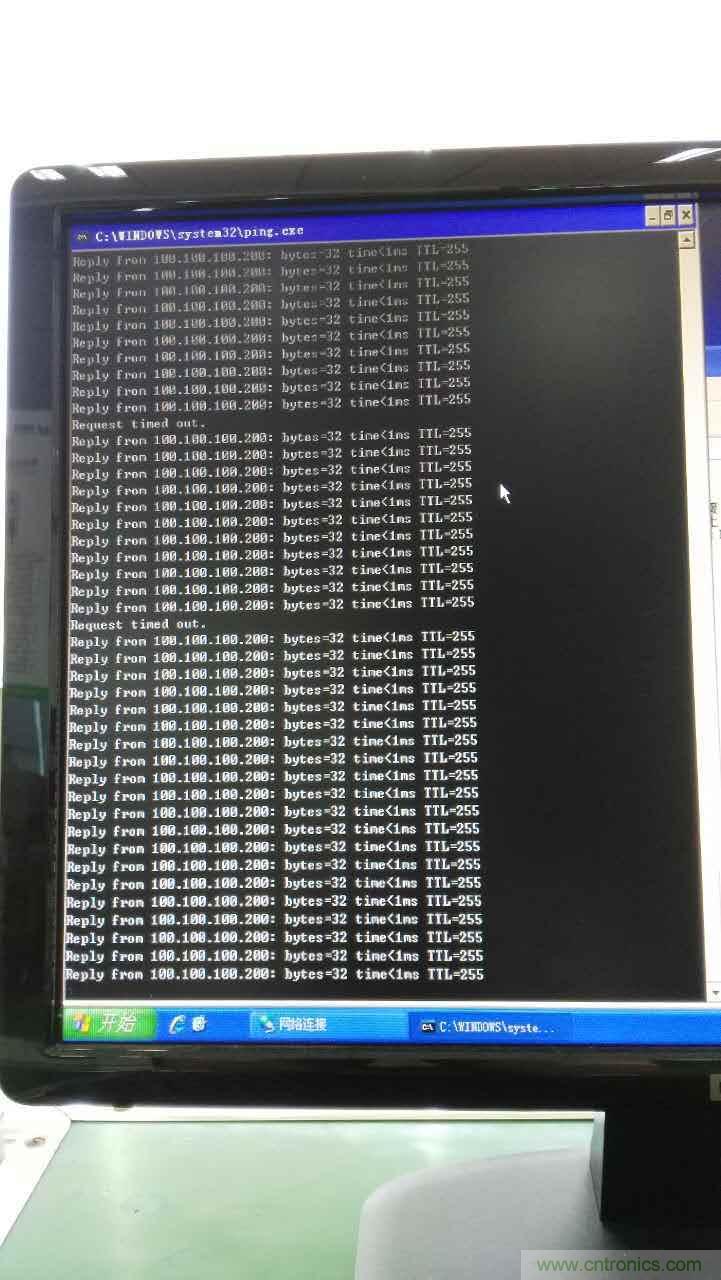

【導讀】上海雷卯電子工程師在負責電力行業的智能采集終端項目升級時,即根據客戶的新需求和國網、南網新標準對原設計進行改進。在做原產品的靜電(ESD)抗擾度4級試驗,即接觸放電±8kV時,發現以太網會中斷,直到ESD干擾消除后才能恢復正常,如圖1所示,這種現象不滿足國網、南網標準中“實驗過程中,以太網偶爾中斷,但能自行恢復”的規定,CLASS B的要求。

圖1:以太網中斷不能重連

有ESD設計經驗的人一般都知道靜電干擾途徑主要為地傳導、信號線+電源線+I/O線傳輸和空間輻射三種。針對以上三種干擾改進ESD設計的方法如下:

1)軟件復位設計。增加軟件看門狗,主循環壞死就reset;加狀態檢測判斷寄存器/IO口狀態是否正確,不對就reset。

2)增加保護目標ESD免疫力,即增強IC本身ESD防護能力,比如內置集成ESD。

3)降低減弱ESD放電對保護目標的沖擊強度,比如在IC外圍增加TVS管和防靜電管等ESD防護器件,割地處理,對地并電容,及縮短走線距離等。

首先以太網芯片屬于公司大批量使用的通用芯片,不應替代;其次軟件看門狗/reset都已經做了處理,所以方法1和2都不可選,只能選擇方法3。查看老版原理圖發現原設計并未對以太網模塊做所需的防ESD處理,只是在數字電源VCC和模擬電源AVCC上加了TVS管,而關鍵的差分信號TX+/TX-和RX+/RX-并沒有設計ESD防護,所以需在差分信號端增加4個TVS管。

TVS管選型需要考慮以下因素:

1)大批量供貨需考慮成本,一般而言,TVS管陣列比增加4個TVS管便宜;

2)封裝小,節省Layout空間,方便布局,TVS管陣列會比4個TVS管的體積小很多;

3)ESD防護能力,必須大于國網、南網靜電抗擾度4級,即接觸放電±8kV,空氣放電±15kV;

4)負載電容越低越好,能快速吸收ESD干擾。

經過查詢資料選用

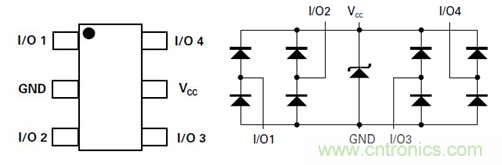

1)封裝極小,1.6mm*1.2mm,封裝和內部結構示意圖如圖2所示;

2)超低負載電容,0.85pF,可將快速信號衰減程度降至最低水平;

3)ESD防護能力高,接觸放電±15kV,空氣放電±15kV,遠高于國網、南網標準;

4)極低的動態電阻,提供超低箝位電壓;超低漏電流,3.3V時最大1nA電流;

5)以太網電源AVCC設計上能節省一個TVS管;

6)價格便宜。

圖2:LEIDITECH ULC0504T6封裝和內部結構示意圖

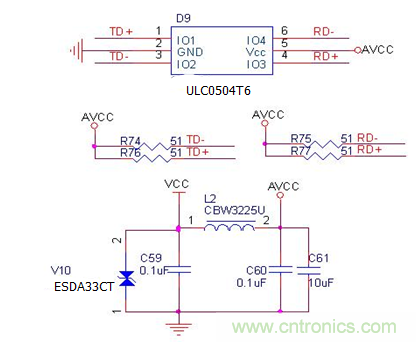

以太網防靜電部分設計原理圖如圖3所示,L2、C59、C60組成π型濾波網絡,C61為去耦電容,R74-R77為以太網傳輸信號的上拉電阻,V10為TVS管,D9為TVS管陣列。

圖3:以太網防靜電部分電路

增加TVS管陣列ULC0504T6后,以太網模塊在Layout設計時需注意以下幾點:

1)ULC0504T6、濾波電容等ESD防護器件盡量和以太網芯片放在同一層,且盡量在同一層將它們的地pin與以太網芯片的地pin,這樣能減少環路面積,讓所包含的場流量減小,其感應電流減小。

2)ULC0504T6、濾波電容等ESD防護器件要靠近以太網芯片放置,差分信號和電源的走線先經過ESD器件pin再到以太網芯片pin;

3)要盡量保證地平面連續,該打過孔的地方要打過孔,以增加回流路徑;

4)以太網模塊不要靠近整個板件的邊沿,盡量往中間放,這樣能增強水平和垂直耦合靜電抗擾度能力。

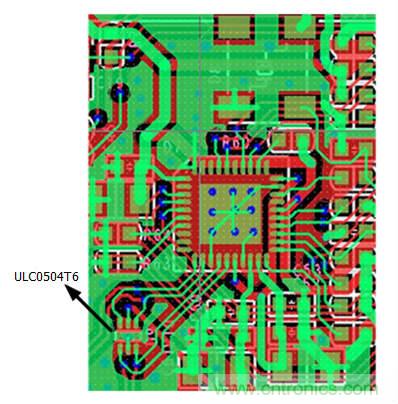

具體PCB布局如圖4所示,由于以太網差分信號從下面上來,所以ULC0504T6放在左下角,這樣保證了信號線先經過TVS管陣列再到以太網芯片pin上。

圖4:以太網layout設計

改進后的設計,靜電實驗結果如圖5所示。實驗過程中偶爾斷一次,但能立刻恢復,滿足了國網、南網靜電抗擾度4級實驗要求。

圖5:改進設計后的靜電實驗結構

推薦閱讀: