【導讀】在通信系統中,各種協議和接口經常讓剛接觸不久的同學迷糊半天。不同領域涉及的通訊類型和應用設計又有一定的差異,因此有必要盡可能詳細的做一下相關知識點的梳理和總結。

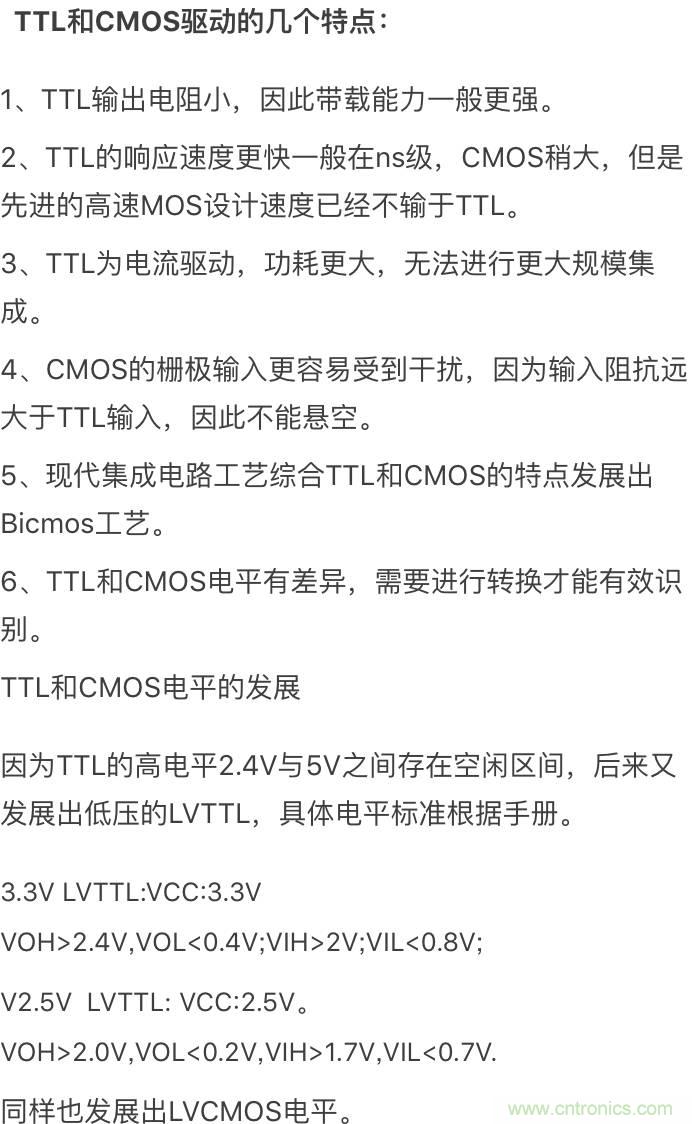

關于電平標準的由來:

在以高(1)和低(0)為格式的數字通信過程中必然要涉及到高和低對應的模擬電壓值,而這個值的確定是有原因和歷史的。具體而言就是和半導體器件的發展有關,例如TTL即Transistor-Transistor Logic (晶體管-晶體管邏輯集成電路),這是因為半導體器件中最先發明的是雙極型晶體管。而后由于MOS,CMOS工藝的發展給電路的供電需求帶來新的改變而導致輸出數字電平標準的變化。

一、TTL和CMOS電平介紹

TTL電路只能在5V或以下工作,VCC=5V時。

TTL 輸出:VOH>2.4V,VOL<0.4V。

輸入:VIH>2.0V,VIL<0.8V。

CMOS電路的工作電壓范圍更寬,可達到12V,VCC=5V時。

CMOS輸出:VOH>4.99V,VOL<0.01V。

輸入:VIH>3.5V,VIL<1.5V。

可以看出TTL電平的噪聲容限為0.4V,CMOS的噪聲容限為1.5V。

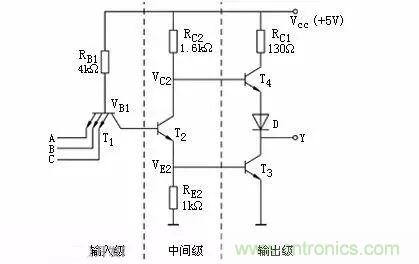

TTL和CMOS門電路結構:

如圖TTL門結構,輸出級采用推挽式輸出結構,T4為射極跟隨的形式,輸出電阻小,帶負載能力強。

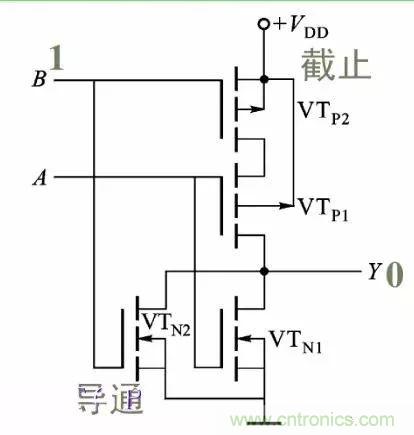

如圖CMOS門結構。

3.3V LVCMOS:Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。2.5V LVCMOS:Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。

二、高速電平標準

在高速電路中如何實現高速驅動輸出呢?要么增大驅動電流,要么降低電平標準,或者提高晶體管工作速度。顯然前者會帶來非常大的功耗,因此改變電平標準和改進晶體管設計成為選擇,雖然低電平更容易受到干擾,所以需要更嚴格的硬件設計。

1、ECL和PECL電平接口

ECL即射極耦合邏輯(Emitter Coupled Logic)采用的是差分結構輸出,并需要負電源供電。后來發展處PECL,即正電源射極耦合邏輯?;驹砭褪抢镁w管工作在非飽和區來減小轉換時間,大大提高轉換速度。

ECL的輸出管始終有電流通過,非常有利于高速轉換。輸出阻抗幾歐姆,輸出電流10mA左右,驅動能力強。

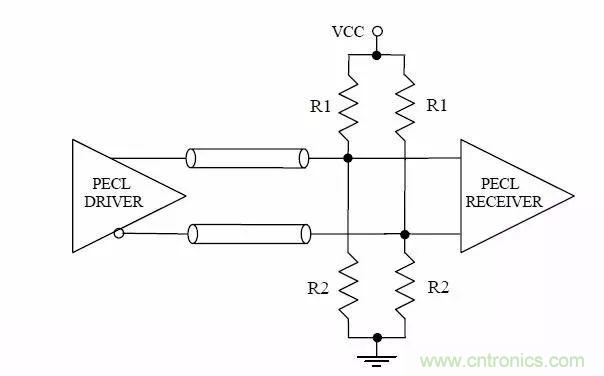

接口連接:直流耦合,適用于短距離

這個匹配方式由等效而來,具體阻值計算:

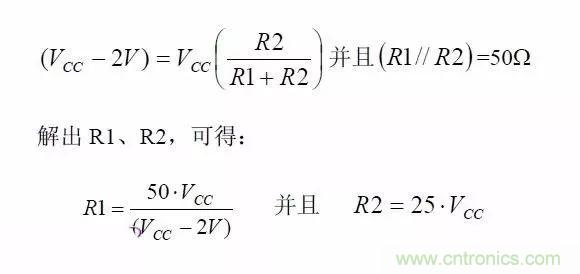

接口連接:交流耦合,適用于較遠距離

2、LVDS電平接口

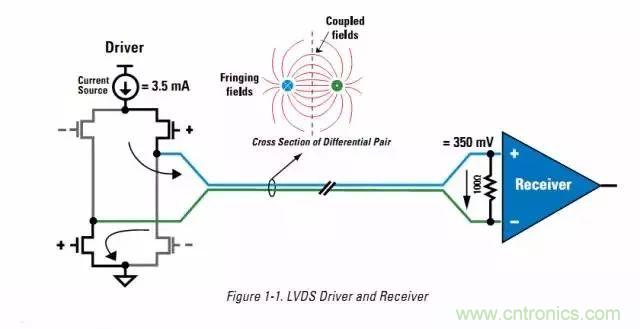

LVDS即Low-Voltage Differential Signaling,是一種利用低壓差分信號傳輸高速信號的電平標準。特點是:低壓,低功耗,噪聲抑制能力強。

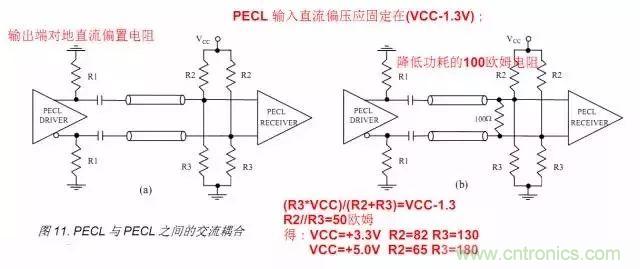

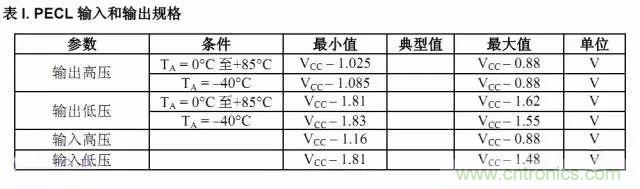

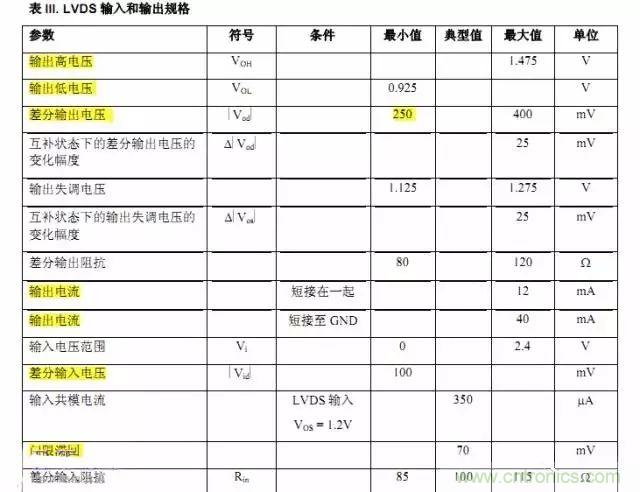

如圖LVDS的輸入和輸出規格:

LVDS的連接方式:直接連接,因為片內具有端接電阻。

三、CML電平接口

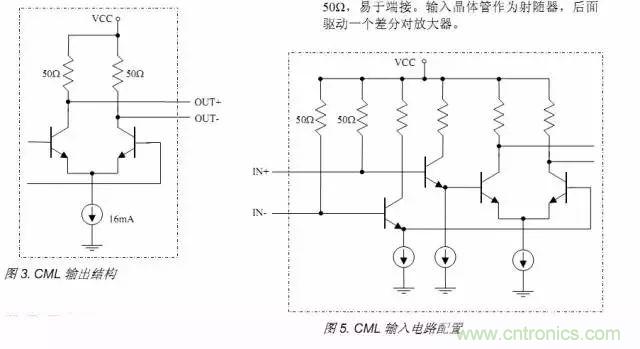

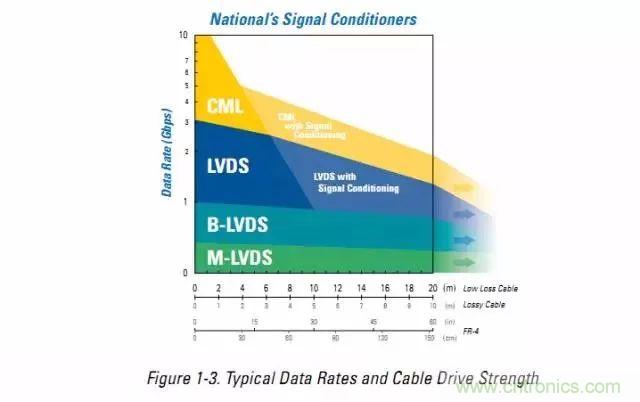

CML即電流模式邏輯電平,采用恒流驅動,內置匹配電阻,使用簡單,短距離高速應用中最多。

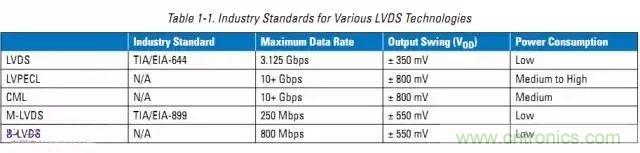

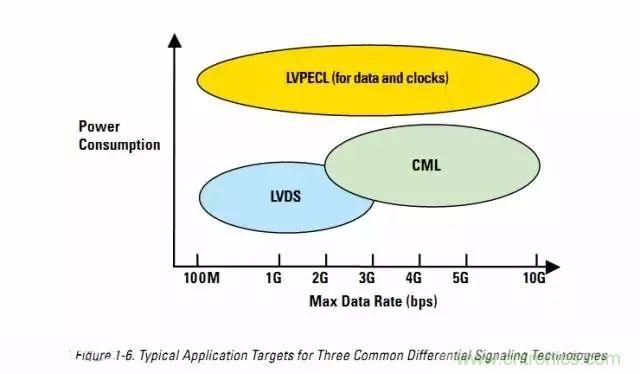

下圖是幾種高速接口的性能簡單比較:

四、常用普通電平標準

在工業領域應用最多的應該是485 232的電平標準,兩者各有優缺點,成本低,使用也比較簡單,但是依然有很多技術要點可以討論,譬如傳輸速度,距離,防護設計等等。

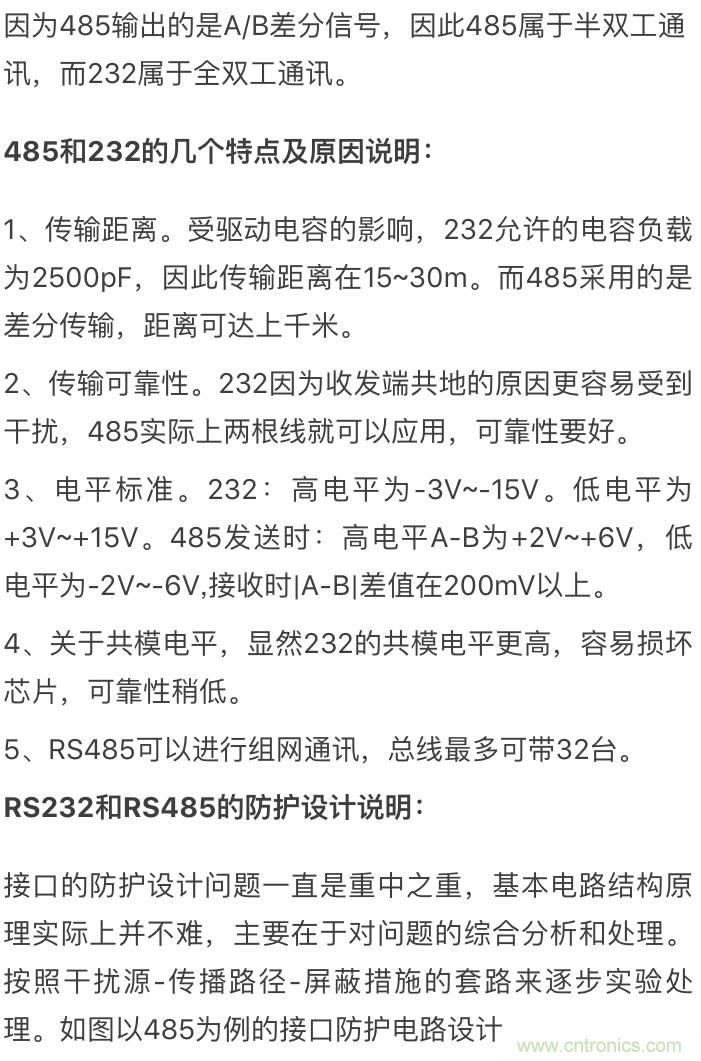

RS232和RS485的連接問題:

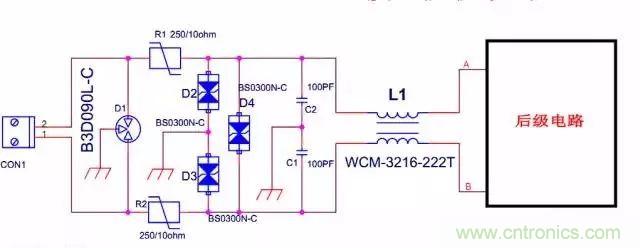

工作中了解到不少同學對于232或者485的連接一直有些迷糊,關于信號的收發端定義及公母頭連接,一開始我也是經常摸不著頭腦。以收發地三線為主。

標準的232是DB9接頭:

簡記為:235-收發地。

485如何利用DB9連接:

485的兩根線對應DB9頭的1,2腳。

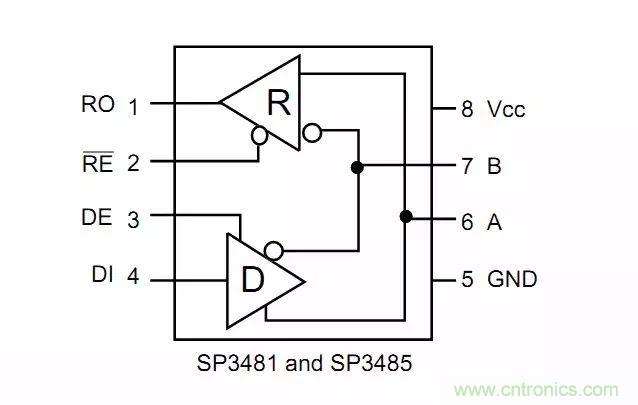

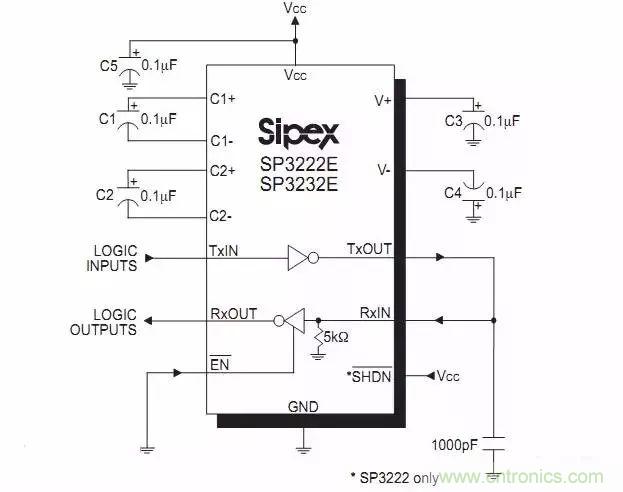

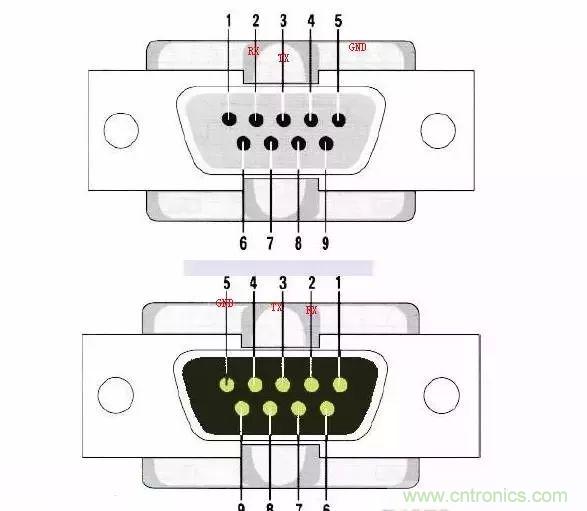

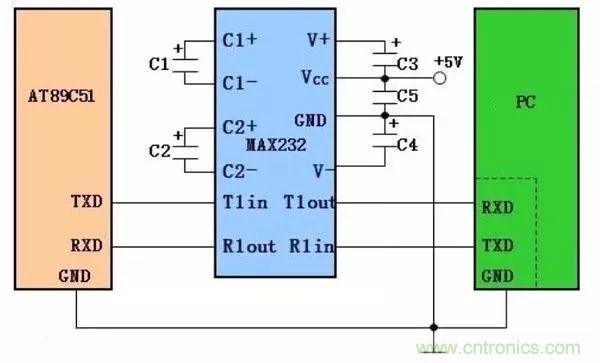

232和485與MCU的連接:

四、小結

關于數字電平的標準主要就這么幾種,這些都是在硬件層面的定義,在軟件上對應的就有各種協議通訊方式的規定。關于接口設計確實是電路設計中的重點,尤其是在目前的高速數字通訊應用當中,我覺得主要有幾個要掌握的方面:

1、信號電平的應用電路,也就是基本結構要清晰。

2、防護設計問題要考慮周全,不同接口對于負載對于匹配度的要求都不一樣。

3、PCB設計的重要性,在高速設計中很多都采用EDA軟件仿真的方式來協助查找關于干擾的問題,但是首要的還是要嚴格遵循相關規則和規范來設計。

4、實驗的必要性。尤其是接口的干擾問題,盡可能全面的實驗方案設計是盡快解決問題的最佳路徑之一。

總之,理論基礎要有,設計考慮要到,測試實驗要全,如此,結果可能才好!

推薦閱讀: