【導讀】某產品采用金屬外殼,對其進行ESD測試時,發現一螺釘位置對ESD及其敏感,對螺釘進行接觸放電4kV,就會發現該產品中的某一PCB出現復位現象。經過觀察分析,靠近敏感螺釘位置有一芯片,芯片上有約2.5cm高的散熱器,該散熱器并沒有采取任何接地措施。在測試中,將散熱器臨時去掉后,該落螺釘位置的抗靜電干擾能力達到了±6kV。

【現象描述】

某產品采用金屬外殼,對其進行ESD測試時,發現一螺釘位置對ESD及其敏感,對螺釘進行接觸放電4kV,就會發現該產品中的某一PCB出現復位現象。經過觀察分析,靠近敏感螺釘位置有一芯片,芯片上有約2.5cm高的散熱器,該散熱器并沒有采取任何接地措施。在測試中,將散熱器臨時去掉后,該落螺釘位置的抗靜電干擾能力達到了±6kV。

【原因分析】

靜電放電時,在很短的時間內會產生幾十安的電流,而放電電流脈沖的上升在小于1ns之內完成,根據脈沖波最高諧振頻率計算公式:

(Tr為脈沖上升時間)

可知,靜電放電的過程是一個高頻能量的釋放與傳輸過程,在傳輸的路徑中一切敏感的線路或器件都將受到干擾,引起設備的誤動作。

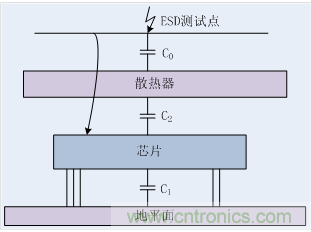

在此案例中,由于靜電放電信號的高頻譜特性使一些因結構特性形成的寄生電容不能忽略不計。圖1是靜電干擾傳輸路徑及原理圖。

圖1中,C0表示測試點與散熱器之間的寄生電容,C2表示散熱器與芯片之間的寄生電容。靜電干擾將從測試點同桂平C0,再經過C2進入芯片內部電路,從而從產品系統中表現出干擾現象。散熱器的存在將大大增加測試點與芯片之間的容性耦合度,因為一方面散熱器有著比芯片更大的表面積;另一方面散熱器的存在縮短了與測試點表面積的距離。因此去掉散熱器后,產品抗ESD能力增強。

圖1靜電干擾傳輸路徑與原理圖

【處理措施】

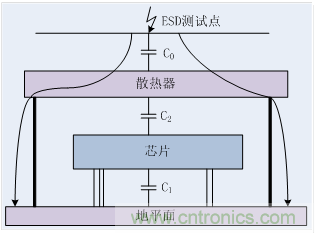

經過以上的分析,只要將散熱器接至地平面就可以了改變ESD干擾的傳輸路徑,從而使芯片受到保護。圖2箭頭曲線表示散熱器接地后的ESD傳輸路徑。

圖1改進后的靜電干擾傳輸路徑與原理圖

【思考與啟示】

對于PCB上的金屬體,一定要直接或間接地接到地平面上,不要懸空。另外,對于較敏感的電路或芯片,在PCB布局時盡量遠離ESD放電點。

以上內容轉載自賽盛技術。

推薦閱讀: