【導讀】大家如果心細的話應該會留意到本期文章的題目,串擾案例分解,已經可以揭示上期問題的答案了,主要是串擾在作怪,原來如此,是不是恍然大悟?

從截圖可以看到,本設計的問題主要有3點:

1、疊層設計不合理,信號與信號之間的間距比信號到參考的間距還??;

2、雙內層走線沒有避免平行走線的問題,而且能避開的區域也沒有意識去避開,以上兩點造成的直接影響就是串擾很大;

3、板子本身比較厚,這樣靠近表層的信號勢必Stub很長,影響阻抗及回損。

解決該串擾最直接有效的方法是優化疊層,尤其是這種過多個連接器的背板設計。

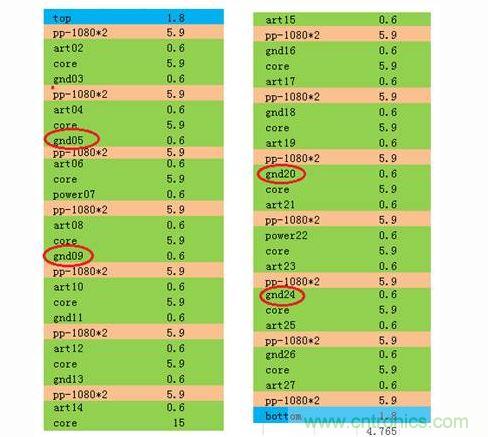

要想完全消除串擾影響,最好就是加參考層,能一層信號一層參考是最好不過的,這也是多數背板的疊層設計方案,當然,成本會有一定的增加。優化后的疊層如下圖一所示。

圖一 優化后的疊層

上面的解釋用仿真其實也是可以驗證的。

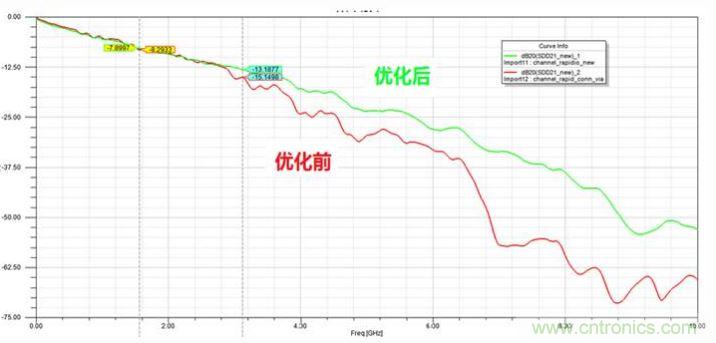

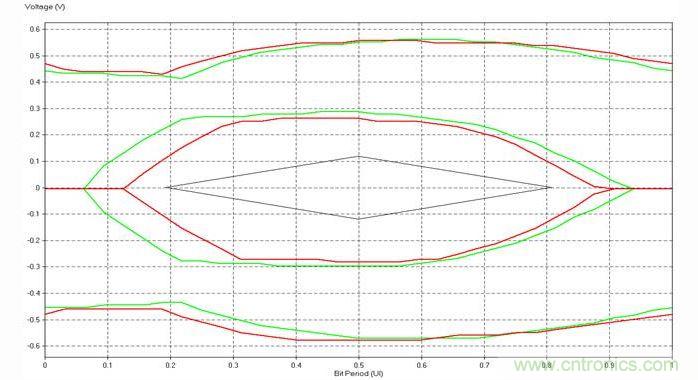

另外對過孔也進行一定的背鉆等優化處理,分別提取優化前后單對通道(不考慮串擾)和多對通道的模型(考慮串擾),然后進行通道無源及有源眼圖仿真,單通道的仿真結果對比如下圖二和圖三所示。

圖二 優化前后通道插損對比

圖三 優化前后通道眼圖對比

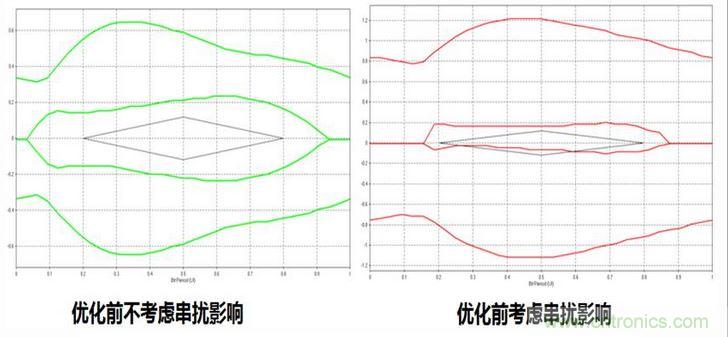

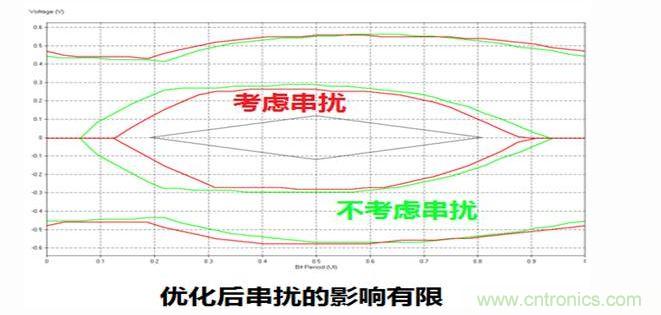

從以上單通道的仿真也可以說明,優化前雖然性能會差一點,但如果不考慮串擾的話單通道眼圖還是滿足要求的,這也可以解釋插幾個槽位還是可以工作的。我們再來仿真下考慮串擾的情況,仿真對比如下圖四所示。

圖四 優化前后考慮串擾的眼圖對比

從圖四可以看出,一旦考慮串擾,也就是多個插槽同時工作的時候,原始設計的背板因為串擾的原因眼圖已經不滿足要求了,而經過優化后即使考慮串擾,也就是多個插槽同時工作都不會對眼圖有太大的影響,眼圖照樣滿足要求,也就是系統照樣正常工作。

經過后期的實際測試,此背板問題最終得到了解決。