【導讀】ECL電路(即發射極耦合邏輯電路Emitter-Couple Logic)是一種非飽和型的數字邏輯電路,電路內晶體管工作在線性區或截止區,速度不受少數載流子的存儲時間的限制,所以它是現有各種邏輯電路中速度最快的一種, 能滿足高達10Gbps工作速率。最先由Motorola公司提出ECL標準。ECL 的主要分類如下。

PECL VCC=5.0V,VEE=0.0V

LVPECL VCC =3.3V,VEE =0.0V

VCC =2.5V,VEE =0.0V

NECL VCC =0.0V,VEE =-5.2V

LVNECL VCC=0.0V,VEE =-3.3V

VCC =0.0V,VEE =-2.5V

PECL即Positive Emitter-Couple Logic,也就是正發射極耦合邏輯的意思,使用5.0V電源。PECL 是由ECL 演變而來的,ECL 即Emitter-Couple Logic,也就是發射極耦合邏輯。ECL 有兩個供電電壓VCC和VEE。當VEE接地時,VCC 接正電壓時,這時的邏輯稱為PECL;當VCC 接地時,VEE接負電壓時,這時的邏輯成為NECL,VEE一般接-5.2V電源;一般狹義的ECL 就是指NECL。由于PECL/LVPECL可以和系統內其他電路共用一個正電源供電,所以PECL/ LVPECL相對于ECL應用更為廣泛。起初的PECL器件是將VCC接+5V,后來為了直接利用廣泛使用的3.3V和2.5V電壓,出現了VCC=3.3V/2.5V的LVPECL(Low Voltage PECL)。

PECL/LVPECL電路結構

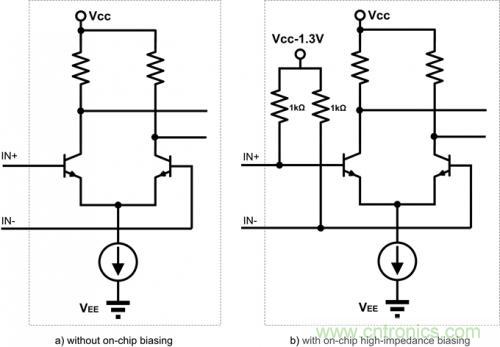

PECL 的輸入是一個具有高輸入阻抗的差分對,該差分對的共模電壓需要偏置到VBB =VCC-1.3V,這樣允許的輸入信號電平動態最大。對于不同芯片的輸入級,信號允許的共模電平可能會有些差異,請參考相應的datasheet。有部分芯片在內部已經集成了偏置電路,使用時直接連接即可,有的芯片沒有加,使用時需要在芯片外部加直流偏置。

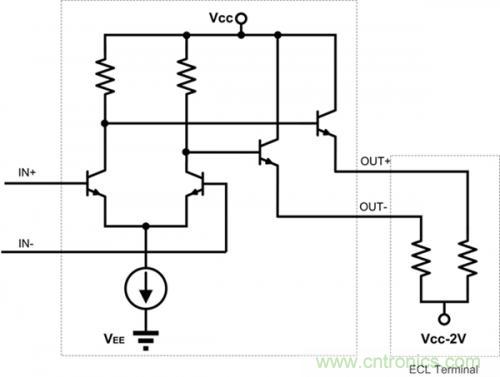

PECL的標準輸出負載是串聯50ohm至VCC-2V的電平上,在這種負載條件下,OUT+與OUT-的共模電壓是VBB=VCC-1.3V,OUT+/OUT-的輸出的平均電流為14mA。

ECL電路優缺點

1、ECL 邏輯的優點:

1)扇出能力強。ECL輸出阻抗低(6~8ohm),輸出阻抗高(通常為10kohm),所以扇出系數很高。

2)噪聲低,對電源要求低。ECL/PECL器件對電源電壓的同步變化是不太敏感的,因此可以在ECL某些應用中相對地放松對電源波紋、偏差和分配的要求。有時允許電路的電源電壓范ECL圍可寬至10%。由于差分電路兩臂交替工作,電路工作時電源電流基本上恒定(不隨邏輯狀態變化而變化,也不隨工作頻率增加而增加),因此可以考慮放寬對電源內阻的要求。

3)速度快。晶體管工作時不進入飽和狀態,只工作在線性區和截止區,沒有少數載流子的存儲現象,開關時間大為縮短;集電結電容大大減小,RC時間常數也相應減小,電路的傳輸延遲時間就很短;電路的邏輯電平擺幅?。▎味诵∮?50mV),在動態轉換過程中各個結上的電壓變化對結電容(包括寄生電容)的充放電時間很短。

2、ECL 邏輯的缺點:

1)ECL的缺點也很明顯,那就是功耗大??梢哉f,ECL 的高速性能是用高功耗為代價換來的。

ECL信號互連

ECL邏輯的高低電平之差一般為800mV,其中心參考電平(共模電壓)VBB根據VCC變化,一般為VCC-1.3V。因此,PECL的電平隨VCC的不同而不同。如:

PECL:

VBB=5V-1.3V=3.7V,VOH=4.1V,VOL=3.3V;

LVPECL:

VBB=3.3V-1.3V=2V,VOH=2.4V,VOL=1.6V;

VBB=2.5V-1.3V=1.2V,VOH=1.6V,VOL=0.8V;

NECL:(VEE =-5V、-3.3V、-2.5V;VCC=0V),

VBB =0V-1.3V= -1.3V,VOH = -0.9V,VOL =-1.7V。

當然,以上的直流特性只是對一般而言,實際上到具體的器件上還是會稍有不同,同一器件的輸入和輸出也不一樣。在設計的時候,都應該參考相應器件的datasheet來獲得其準確的電氣特征。

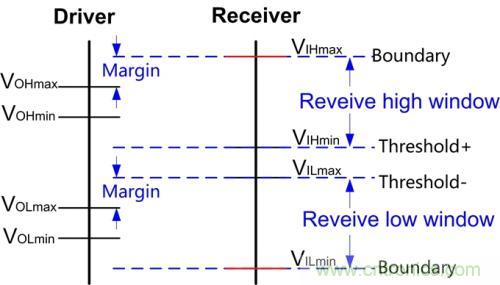

關于直流特性,還有很重要的一點就是兩個ECL器件之間的接口匹配,也就是說,我們要特別關注Driver的輸出是否在Receiver的輸入的容差范圍之內。我們稱這個容差范圍為“接收窗口”。如果Driver的輸出沒有落在這個接收窗口之內,就有可能造成接收端的誤判,從而造成設計上的失敗。

因此看兩個ECL器件是否能夠互連,對于Driver,只要是從DATASHEET中得到其輸出高電平VOH和輸出低電平的VOL的范圍;對于Receiver,只要看其關于接收窗口的一些指標,分兩種情況。

1、單端信號

如果ECL用作單端信號的話(這種情況并不多見),互連分析得方法與LVTTTL,COMS等單端信號的方法類似。

需要關注的是輸入高電平VIH和輸入低電平VIL的最大和最小值,VIH的最大和最小值構成了VIH的接收窗口,VIL的最大和最小值構成了VIL的接收窗口。如下圖:

當Driver的VOH范圍全部落入Receiver的VIH窗口之內,Driver的VOL范圍全部落入Receiver的VIL窗口之內時,可以保證Receiver可以正確接收Driver的輸出,否則會有潛在的互連不正確甚至損壞器件的可能。

2、差分信號

對于差分信號,要關注的指標是輸入共模電平VCM和差分信號VDIFF范圍。

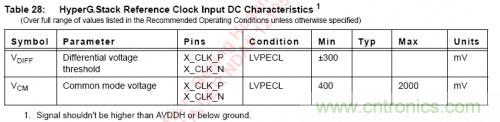

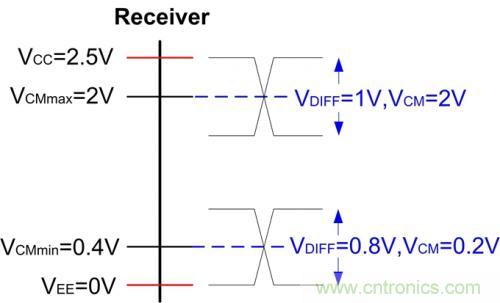

如某器件的某輸入口工作在LVPECL模式下。其指標如下(AVDDH=2.5V):

那么其接收窗口如下圖所示,圖中標出了共模電壓為最大或者最小時,其允許的最大單端電壓。

只要落在這個范圍內的差分信號,即同時滿足:

1.輸出|VDIFF|大于300mV;

2.輸出共模信號VBB位于400 mV到2000mV之間;

3.輸出的單端信號不能超過VCC或者VEE;

滿足以上條件的差分信號都可以被正確接收??梢宰⒁獾?,如果共模信號被端接到VBB =VCC-1.3V,接受窗口最大。

由上可見,差分信號有比單端信號寬得多的接收窗口,這也是高速應用中差分信號被普遍采用的原因之一。